# FAST data acquisition at Cosmo-Z board

Jiří Záhora

- 8 channels of 12-bit 125MHz ADC

- XILINX's FPGA "ZYNQ"

## Why FPGA

- Field-programmable gate array

- It's fast

- Signal processing during acquisition

- Reducing amount of data

## Math restrictions for HW implementation

- Easy operations

- add, substract, multiply, divide 2<sup>n</sup>

- Difficult operations

- general division, square root

Trigger condition:  $\frac{\operatorname{fir}(sig) - \operatorname{mean}(nsb)}{\operatorname{stdev}(nsb)} > threshold$

#### Rewrite for FPGA implementation:

$(\operatorname{fir}(sig) - \operatorname{mean}(nsb))^2 > threshold \cdot \operatorname{var}(nsb)$

## Next steps

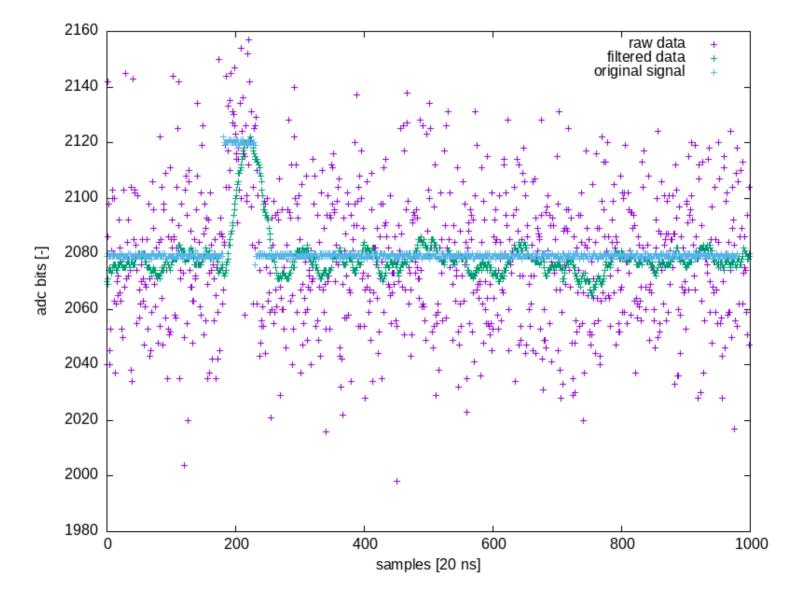

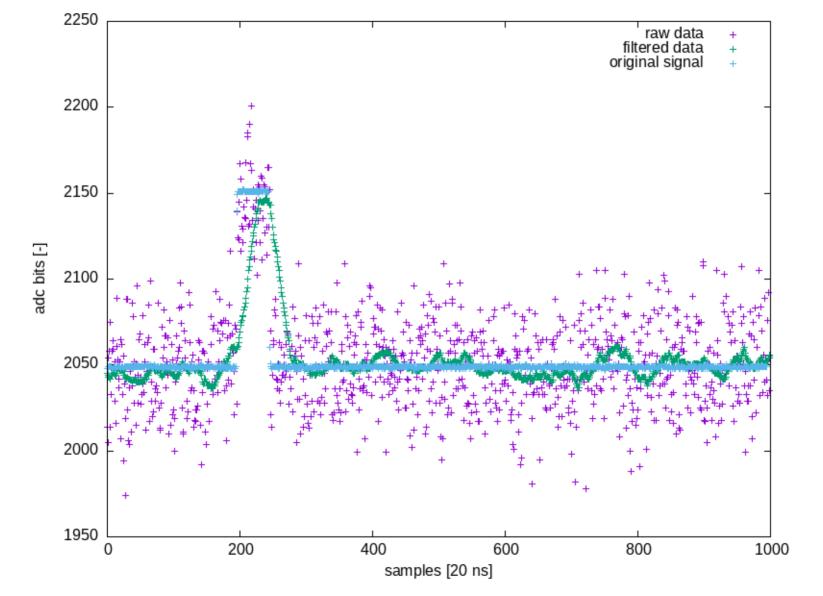

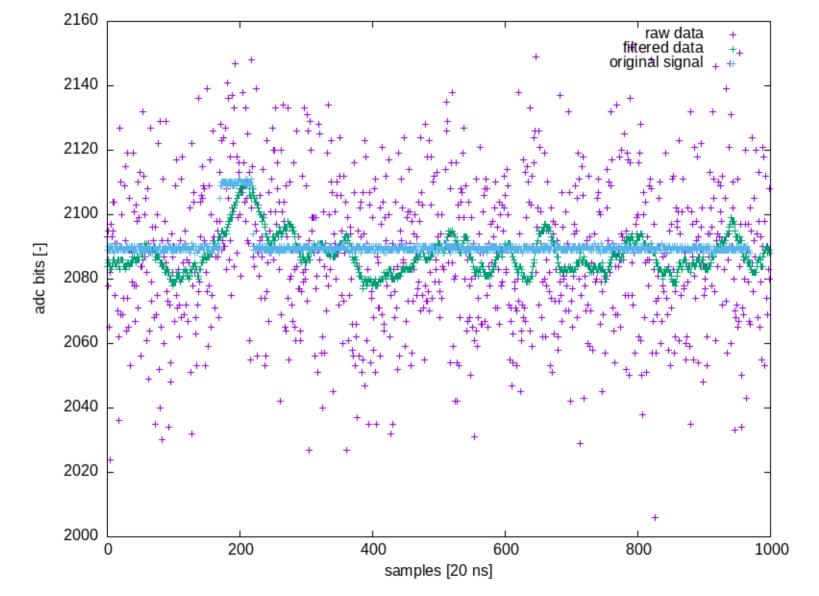

- Better signal filtering

- Currently moving average filter (width = 64)

- Implement FIR filter, different widths, thresholds

- Rewrite code for better parametrization

- Add GPS timestamps

- Repair broken board

### Thanks for attention